国内科研团队在二维高性能浮栅晶体管存储器方面取得重要进展

浮栅晶体管作为一种电荷存储器,是构成当前大容量固态存储器发展的核心元器件。然而,当前,商业闪存内硅基浮栅存储器件所需的擦写时间约10μs-1ms范围,远低于计算单元CPU的数据处理速度(~ns) ,而其循环耐久性约为105次,也难以满足频繁的数据交互。随着计算机数据吞吐量的爆发式增长,突破传统浮栅晶体管擦写速度、耐久性等瓶颈,发展一种可兼顾高速、耐久特性的存储技术势在必行。

二维材料具有原子级厚度和无悬挂键表面,在器件集成时可有效避免窄沟道效应和界面态钉扎等问题,是实现高密度集成、高性能闪存器件的理想材料。然而,此前研究中,其数据擦写速度多异常缓慢,鲜有器件可同时实现高速和高循环耐久性。

针对这一挑战,该研究团队提出了一种具有边缘接触特征的新型二维浮栅晶体管器件,如图2所示,利用MoS2材料内独特的1T/2H金属-绝缘体相变工程在传统二维浮栅晶体管器件内引入边缘接触实现了擦写速度在10-100ns、循环耐久性超过3×106次的高性能存储器件。研究中,团队利用化学Li+插层手段,对传统金属-半导体接触区域内MoS2进行相转变,使其由半导体相(2H)向金属相(1T)转变,使器件内金属-半导体接触类型由传统的3D/2D面接触过渡为具有原子级锐利界面的2D/2D型边缘接触。

团队在长期的研究中发现,这种接触模式可有效避免接触势垒钉扎,从而有利于晶体管内通过金-半接触产生热电子注入,促进浮栅晶体管内电荷擦写效率的提升,在7-15V较低的工作电压和超短的脉冲下完成浮栅电荷的擦写,保证器件的循环耐久性。

通过对比传统面接触电极与新型边缘接触,该研究说明了优化制备二维浮栅存储器件内金属-半导体接触界面对改善其擦写速度、循环寿命等关键性能的重要作用。

据悉,华中科技大学材料学院、材料成形与模具技术全国重点实验室翟天佑教授团队题为“基于相变边缘接触的高速、耐久二维浮栅存储器”的研究论文已于9月14日发表在国际学术期刊《自然通讯》(Nature Communication)杂志在线。

站内头条

-

第二十二届中国国际半导体博览会(IC China 2025)在北京国家会议中心开幕

2025-11-27 -

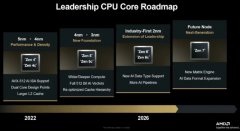

AMD发布 “领导力 CPU 核心路线图” 的 Zen 架构演进规划

2025-11-13 -

市场监管总局、工业和信息化部联合发布首批计量“十大重点项目”

2025-11-13 -

AMD CEO苏姿丰:2030年AI数据中心市场将超1万亿美元

2025-11-12 -

台积电10月营收达3674.7亿元新台币

2025-11-11